System Architecture

The CONCEPT 32/97 computer is built around a high-speed synchronous

bus called the SeIBUS that has a transfer rate of 26.67 million bytes

per second. The CPU, PU, main memory and the input/output subsystem

reside on the SeIBUS as shown in Figure 1.

CPU/IPU

The CPU and IPU are implemented with the MC 10,000 series Emitter

Coupled Logic (ECL) which provides extremely fast gate switching times.

Functional units within the CPU and IPU are connected by internal busses

which have 75-nanosecond bus cycle time.

During each 75-nanosecond cycle, four macroinstructions are in

various phases of execution. This pipelined method of operation

increases the effective throughput of the CPU and IPU and, hence, the

system

Interrupts/Traps

Assigned to devices external to the CPU, are 96 interrupt levels that

report real-time events to the software. The notification of these

events are prioritized, scheduled and in some cases, deferrable.

Interrupts must contend for recognition by the CPU as only the highest

priority interrupt is recognized and executed by the CPU.

Interrupt levels are assigned to individual SeIBUS devices (i.e I/0

channels, Real-Time Option Modules (RTOM) and the Input/Output Processor

(lOP). The real-time clock and the interval timer interrupts use one

level each Users requiring more external interrupt lines can add one or

more RTOMs. Each provides 16 external interrupt levels.

Traps are error conditions that are identified and reported by the

CPU/IPU. All traps have the same priority with the exception of the

power fail trap, which overrides all other traps and interrupts

Input/Output Processor (lOP)

The lOP, a powerful multiplexing channel for I/O operations, resides

on the SeIBUS and operates independently of and in parallel with the

CPU. The result is increased CPU availability and improved system

performance.

Under the control of the lOP the Multipurpose (MP) Bus, a medium

speed asynchronous I/O bus, transfers data at a rate of up to 1.5 MB per

second. Up to 16 device controllers supporting up to 124 devices can be

handled on a single MP Bus by a single lOP. Larger systems can use

multiple lOPs to implement additional MP Buses.

Diagnostic Processor

The Diagnostic Processor has four main functions:

• Loading the CPU/1PU control store at power-up

• CPU/IPU self-test

• Diagnostic tool

• Remote diagnostic

At power-up, the Diagnostic Processor loads the CPU and the IPU

microdiagnostics from a dedicated floppy disc to the control store RAM.

It then performs CPU and the IPU tests before loading the CPU/IPU

microcode and system initialization.

The non-critical modules, such as the MACC, the cache banks or the

Shadow Memory, are placed off-line if a failure is detected at power-up.

In a dual-processor (CPU/IPU} configuration, the failing processor is

placed off-line and the remaining processor is reconfigured as the CPU.

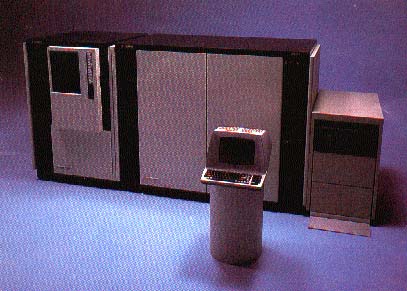

Control Console

The Control Console combines the operator’s console function the

control panel functions. It is connected to the Diagnostic Processor

Control Console Port, which, with modems, permits remote control of the

system.

The Control Console has three modes; Operators Console mode, Control

Panel mode, and Diagnostic mode. The operator can switch between the

three modes at any time using the key switch. Operator’s Console mode

is the normal mode for the control Console when the system is running.

Job status, user status, and operator information are displayed. The

operator can monitor and control operation of the system. In the

Operator’s Console mode, the CRT also functions as a user terminal.

Control Panel mode displays status and allows the operator to display

and/or modify Machine State, General-Purpose Register contents memory

locations. The system is in Diagnostic Mode when first powered up. .CPU

microdiagnostics can be run, single-stepped, and halted from Control

Console, which displays relevant information on the status of each

diagnostic.

Line Printer/Floppy Controller

The Line Printer/Floppy Controller provides the user an interface up

to two line printers and two floppy disc drives. The floppy discs

double-sided, double-density discs. All Gould CSD line printer are

supported by this controller.

The Line Printer/Floppy Controller is an MP Bus device and is based

on a microprocessor. The microprocessor communicates through MP Bus

interface to the IOP and controls the line printer and the floppy disc

drive through their respective interfaces.

Data buffers in each of the interfaces allow high throughput with

minimum of lOP intervention. Each printer port has a 256 byte buffer.

The floppy disc port has a 2 KB buffer which holds up to eight sectors

of data.

Memory

Airthierachical memory system increases system performance by g that

needed data is available for CPU/IPU usage in a very fast memory. Each

level in figure 2 represents a level in the memory arrachy. Each level

is successively faster than the one below, with CPU/IPU exchanging data

with the system cache.

Main Memory

Main Memory in the CONCEPT 32/97 interfaces directly to the SelBUS.

The Integrated Memory Module (IMM) is a high-density memory subsystem

implemented on a single board It includes up to 1 dynamic MOS RAM,

memory controller, error correction logic, fresh circuitry.

The IMM can overlap two read cycles, allowing reads to be initiated

300 nanoseconds. A write can be initiated every 300 nanoseconds to a

single IMM. When multiple IMMs are used, they can or 4-way interleaved.

Writes can then be initiated every 150 seconds.

The MOS Memory is organized as 39-bit words: 32 bits of data and 7

Error Correction Code bits (ECC). During the write operations, the ECC

bits are generated based on a modified Hamming code algorithm stored in

memory.

When a read memory operation takes place, the ECC bits are checked. A

1-bit error is detected, the error is corrected. Two bit errors and

multiple bit errors with an even number of bits wrong cause an error

dection signal.

Cache

Cache memory is a very high-speed memory. It is integral to the CPU

and IPU, and logically resides between the processor and main memory.

(See Figure 1).

Cache memory reduces the effective cycle time of the memory system

and is transparent to the user. It provides a double word, which

contains two word instructions or four halfword instructions or an

operand, to the CPU/IPU in 75 nanoseconds.

The 32 KB cache memory is structured with four banks of 8 KB each.

The 64 KB cache memory contains eight banks of 8KB each. They use

respectively 4-way and 8-way set associative mapping. A modified Least

Recently Used (LRU) algorithm is used to allocate data to a bank.

A cache control unit fetches data from main memory, monitors SeIBUS

activity, and monitors the relevance of the contents of cache memory. It

also loads the cache memory with requested data from main memory (see

Figure 2) and copies the memory address for that block of data into the

cache index. The cache system performs write throughs to main memory and

monitors writes on the SelBUS to insure that the cache contains an

accurate copy of main memory.

Shadow Memory

The optional Shadow Memory provides a high-speed copy of a region of

main memory. Like cache, access time to this RAM is 75 ns. Unlike cache,

the same addresses are always represented in Shadow Memory.

The addresses contained in cache are a function of the recent history

of the processor utilization. The addresses contained in the Shadow

Memory are hardware assigned. Each Shadow Memory module maps a single

128 KB block of main memory. The CONCEPT 32/97 can support up to 256 KB

of Shadow Memory in both CPU and IPU.

Shadow Memory is initialized either by writing to the shadowed

address range during system initialization or by the processors

microcode during a warm start (main memory backed up by battery power).

Shadow Memory is transparent to the user. I/O reads from the shadowed

addresses occur from the main memory. Writes to the shadowed address

range are updated into the Shadow Memory directly from the SeIBUS. The

Shadow Memory can be used with a region of shared memory. This permits

75 ns access to shared data structures.

Input/Output Subsystem

The dual bus architecture of the CONCEPT 32/97 provides a choice of

I/O performance levels. High performance I/O resides on the SeIBUS,

while medium performance I/O resides on the MP Bus. This two-bus I/O

structure allows great flexibility in system integration.

The basic I/O subsystem of the CONCEPT 32/97 consists of the:

• Input/Output (lOP)

• Diagnostic Processor

• Control Console

• Line Printer/Floppy Controller

Data Types

Instructions manipulate bit-, byte-, halfword-, word and double-word

fixed point operands Floating-point word and double-word operands are

supported by the integral Floating-Point Processor.

Instructions are classified as either halfword instructions (16-bits)

or word instructions (32-bits). The word instructions refer to memory

locations; the halfword instructions deal with register operands. The

functional classification and corresponding number of instructions for

the CONCEPT 32/97 are as follows:

The CPU is capable of both privileged and unprivileged operation.

Privileged operation allows the CPU to perform control functions and I/O

instructions. Unprivileged operation is the normal user program mode of

the CPU. In this mode, memory protection is in effect and all privileged

operations are prohibited. This prevents unprivileged users from

interfering with each other or the system.

The memory protect system provides write protection by individual

protection granules. A protection granule consists of 2 KB. Up to 16 MB

can be protected at a time The memory protect registers can be changed

by executing privileged instruction.

The CONCEPT 32/97 provides two memory addressing environments: mapped

and nonmapped. It also supports two addressing modes: the base register

mode and the non-base register mode.

When in the non-base register mode, two options are available under

each environment: extended and non-extended. The user controls the

selection of the options under each environment. These options determine

the rules for logical address generation.

In the base register mode, the CPU uses eight base registers to

extend the addressing range of a single task. This mode allows 16 MB

addressing for both code and data.

In the mapped environment, the CPU uses 2048 MAP registers to

translate logical address into physical address. The map registers for a

user program are loaded on an as needed basis. There are two banks so

one may be cleared "off line" to minimize context switch time.

The memory is partitioned in 8 KB blocks and the write protect on 2KB

boundaries.

Technology Marketing Group

Technology Marketing Group