GENERAL

The 32/7780 is the first simultaneously on the same system, a benefit

that, until now, only the owners of multi-million dollar main-frames

could obtain.

The higher system throughput made possible by multiple stream

processing meets or exceeds the rigorous performance requirements

demanded by high-end engineering, real-time, and scientific users.

The 32/7780 is a CPU/IPU combination. The CPU is the same powerful

CPU used in the 32/77 computer. The 111-I is an Internal Processing

Unit. Its function is purely computational. The IPU and CPU have equal

computational abilities, but the CPU retains control of I/O and

interrupt operation. The high system throughput that results from this

combination makes the 32/7780 a powerful balanced system.

Both the CPU and the IPU can have their own High-Speed Floating-Point

Unit. The Floating-Point Units provide the CPU and IPU with the ability

to perform floating-point operations with very large operands in a

fraction of the time required by standard firmware floating-point

implementations.

Scientific Accelerators are added to both the CPU and IPU. A

Scientific Accelerator puts Scientific Runtime Library subroutines in

Writable Control Storage boards, connected to the CPU and IPU. Assembly

Language or FORTRAN users experience much faster execution of programs,

since a firmware implementation runs much faster than equivalent

assembly Language programs.

In a multi-task environment of any type, the SYSTEMS 32/7780 computer

proves superior to traditional architectures.

FEATURES

The 32/7780 includes the following features:

• Balanced Architecture

• High-Speed Floating-Point Units

• Scientific Accelerators for FORTRAN

Halfword, Word, or Doubleword Operands

• Multilevel Indirect Addressing

• Eight 32-bit General Purpose Registers

• Regional Processing Units

• Up to 112 Priority Interrupt Levels for I/O, External Interrupts,

and Traps

• MPX-32 Operating System

• Field-Proven Utility and Applications Programs

• Modular Construction for Configuration flexibility

SYSTEM THEORY

Advantages provided to the user by the 32/7708 come in the form of

higher system throughput in both single process and multiprocess

applications.

A traditional computer with a throughput of "X" is show in

Figure 1A. Increasing he speed of that processor will lead to higher

system throughput, but he advantages are small and expensive since the

increase in throughput is inherently additive.

Figure 1B shows the 32/7780 approach. A multiple stream computer can

significantly enhance the system throughput without restoring to

expensive high-speed implementations.

This multiplicative throughput enhancement offers a tangible

improvement over conventional approaches to the problem.

The improvement is immediate. The user’s throughput increases

without any reprogramming. By taking advantage of multiprocess

programming, The user can fully realize the potential of the

architecture by segmenting his program into compute and I/O tasks, and

further improve throughput.

The 32/7780 computer can also be seen as a "gracefully degrading

system" in the event of a processor failure. If the CPU fails, the

user can simply jumper the IPU turning it into a CPU, and start running

again. If the IPU fails, the CPU can keep running without user

intervention. Spares requirements and system downtime are reduced

significantly.

SYSTEM ARCHITECTURE

The 32/7780 is a true Multiple Stream Processor. Two tasks can

simultaneously run on the CPU and the IPU. Both the CPU and IPU have

identical computational capabilities while the CPU handles all I/O and

interrupts.

This balanced architecture allows the programmer to segment

applications, and specify which tasks are to be given to the CPU or IPU.

Instructions not allowed in the IPU will quickly passed to the CPU for

execution.

Although the IPU is transparent to most users, some multitasking

applications can be affected by the concurrent execution of individual

tasks. For example, two tasks which access a shared database may need to

use MPX-32 synchronization primitives (e.g.. Resource Marks), to avoid

inconsistencies in the database. Although the bit manipulation

instructions. ABM, SBM, ZBM do provide automatic synchronization between

IPU and CPU, the Add Register to memory instruction. ARMX does not.

Tasks may also specify that they need to run in the CPU for all or part

of their execution.

The 32/7780 is a high-performance 32-bit computing system built

around multiple high-speed, synchronous, shred, multiplexed buses: The

SelBUS and one or more memory buses (Figure 2). The SelBUS provides the

path for communication between all functional elements of the system. It

runs vertically through the logic chassis and distributes information at

a rate of 26.67 million bytes per second. The modules that plug into the

SelBUS include: the CPU and IPU, High-Speed Floating-Point Units,

Real-Time Option Modules (RTOM), Input/Output Microprogrammable

Processors (IOM) and Regional Processing Units (RPU), which are used as

I/O controllers. The Writable Storage Options also occupy SelBUS slots

but are electrically connected directly to the CPU.

The Memory Bus Controllers (MBA) plug into the SelBUS and control up

to 4 Megabytes of memory on the Memory Bus. The Memory Bus is a separate

Memory chassis.

SelBUS

The SelBUS is a high-speed, synchronous, time division multiplexed

bus that can transfer data at the rate of 26.67 million bytes per

second. Interrupt and SelBUS priority are uniquely definded and are not

module-position dependent. Each module is assigned 1 of the 23 SelBUS

priority lines by simple jumper settings.

The SelBUS is a bi-directional bus. Thirty-two data lines and 24

address lines on the SelBUS are used to send and receive data between

system components. These transfers can occur every 150 nanoseconds. The

address lines are used to select the desired subsystem component or

memory location for a data transfer operation. Both data and address

lines operate simultaneously.

CPU/IPU

The CPU and IPU are each implemented on three plug in boards. Two of

these boards make up the Arithmetic Logic Unit. The third board is the

control unit, which contains the firmware implementing the instruction

set and control logic.

The 32/7780 computers use instruction lookahead for task instruction

execution. Instruction fetches are made concurrently with instruction

execution and with decoding a previously fetched instruction. The

functional difference between the CPU and IPU are shown in Table 1.

REGISTERS

Both 32/7780 CPU and IPU have a set of eight high-speed, general

purpose registers for use by the programmer for arithmetic, logical, and

shift operations. Three general purpose registers –R1, R2, and R3 -

can also he used for indexing operations. Register RO can also be used

as a link register, Register R4 can be used as a mask register.

Instruction Repertoire

The instruction repertoire in the 32/7780 computer includes 187

standard instructions.

The functional classifications and the number of instructions each

class are as follows:

|

CLASS |

CPU |

IPU |

|

Zero

Fixed – Point ArithmeticFloating-Point Arithmetic

Boolean

Load/Store

Bit Manipulation

Shift

Interrupt

Compare

Branch

Register Transfer

Input/Output

Control

Hardware Memory

Management

Writable control Storage

Total |

5

30

8

17

26

8

13

9

11

9

13

11

19

4

3

187 |

5

30

8

17

26

8

13

0

11

913

0

17

4

3

165 |

The eight bit-manipulation instructions provide the capability to

test and set, test and zero, add to, or simply, test any selected bit in

any memory location within 512KB of memory or in any general purpose

register.

Instructions are either halfword instruction (16 bits) or word

instruction s (32) bits. The word instructions primarily reference

memory locations, while the halfword instructions deal primarily with

register operands.

Because approximately one-third of the instructions are halfword

instructions, program memory space is conserved by packing tow

consecutive halfword instructions into a single memory location. The two

instructions are fetched simultaneously. Fewer memory accesses make

programs execute faster.

Hardware Memory Management

The 32/7780 computer operates under the MPX-32 Operating System.

MPX-32 is a mapped executive, and has two ways to address memory:

• Mapped, Nonextended

• Mapped, Extended

Mapped, Nonextended

Mapped, Nonextended addressing allows the CPU and IPU to address any

instruction or operand (bit, byte, halfword, word, or doubleword) within

a task’s logical address space. This space consists of 512 KB of

logical memory dispersed anywhere within the 16 MB physical memory.

MPX-32 allows multiple logical address spaces. A user can access

instructions and operands within the logical address space in which his

task resides. Physical blocks of memory can be common to many logical

address spaces; thus, tasks in different logical address spaces can

share common blocks of physical memory.

Mapped, Extended

Mapped, Extended addressing provides all the capabilities of Mapped,

Nonextended addressing plus access to a extended logical address space.

This space consists of 512 KB of memory beyond the primary logical

address space. It allows the user additional memory space to store data

(operands). Each extended logical address space can be 512 KB long,

dispersed anywhere within 16 megabytes of physical memory. The

combination of primary and extended logical address space supports

programs up to one megabyte long. The executable code must lie within

the primary logical address space but operands can be in either the

primary logical or extended logical address space.

Nonmapped Addressing

The 32/7780 hardware supports two other addressing methods. These are

provided for compatibility with earlier machines and are not supported

by MPX-32. They are:

• Nonmapped, Nonextended-Indexed

• Nonmapped, Extended-Indexed

MEMORY SUBSYSTEM

All 32/7780 Computers include a Memory chassis, a Memory Bus, Refresh

Board, Memory Bus Controller (MBC), and Memory Modules.

The Memory chassis provides slots for up to 16 MOS Memory Modules;

therefore, the inherent memory expansion capability of the 32/7780

computer 4 MB. Expansion to 16 million bytes is accomplished by adding

Memory Support Packages. Each Memory Support package provides an

additional chassis, MBC and power and can support up to 4 MB.

The Memory Modules used in the 32/7780 provide 256K bytes of 600 ns

MOS memory with ECC. The MOS Memory is organized in 39-bit words: 32

bits of data and seven Error Correction Code Bits (ECC). During write

operations, the ECC bits are generated and stored in memory. When a read

memory operation takes place, the ECC bits are checked. If a 1-bit error

is detected, the error is corrected. If two bits are in error, an error

signal is generated.

The MBC in the 32/7780 Computer provides an interface between the

SelBUS and the Memory bus. It can overlap and interleave up to four

memory operations, and can handle one memory request during each

150-nanosecond cycle.

When a system has two memory modules (or any number divisible by

two), memory can be two-way interleaved to provide increased throughput.

Likewise, with four memory modules, memory can he four-way interleaved.

Memory Protect

The Memory Protect system provides write protection for individual

units of memory, called protection granules. A protection granule

consists of 512 words. Up to 256 pages (128K words) can be protected at

a time. The memory protect registers can be changed by executing

privileged instructions. In addition, memory management provides memory

protection for each 32 KB memory block or logical address space. One

protect bit is associated with each 32 KB memory block.

INPUT/OUTPUT SUBSYSTEM

The power and flexibility of the 32/7 780 Computers I/O system is

derived from three sources: intelligent lnput/Output Microprogrammable

Processors (IOM), High-Speed Data interface (HSD). and Regional

Processing Units (RPU). All provide high-speed block-oriented transfers

direct to memory.

The MPX-32 operating system supports 16-Megabyte addressing, command

chaining, and data chaining via extended protocols, to provide a

powerful I/O system. Modem support under MPX-32 adds to the scope of the

1/0 system, providing communications processing capabilities.

The High-Speed Data interface (HSD) is capable of transferring data

at 3.2 megabytes per second. The Regional Processing Unit (RPU) includes

2048 32-bit words of PROM and, optionally, 4096 32-bit words of RAM for

user programmable firmware or data. Special interfaces can be

implemented on the RPU by providing firmware and designing the device

interface, which for the most part consists of matching signal levels

between the RPU’s

Microprogrammable Processor and the device.

The 32/7780 Computer has a total of 12 I/O instructions. Upon

execution of a single instruction, an I/O Controller can be conditioned

to transfer one or more blocks of data between the external device and

memory. Once the transfer is initialized, the controller takes charge of

the I/O operation, and the CPU is free to perform other tasks. When the

transfer is completed, an I/O Controller can notify the CPU by an

interrupt.

Interrupts/Traps

The 32/7780 Computer

can accommodate up to 112 hardware priority interrupt levels used for

I/O Controllers, integrity features, and external signals. The

interrupts associated with the I/O are provided by the I/O

Controllers.

The Real-Time Option

Module (RTOM) provides 18 external interrupt levels, a real-time

clock, and a 32-bit programmable interval timer. The real-time clock

and interval timer each uses one interrupt level.

Each interrupt level

has an assigned dedicated memory location. All interrupt levels,

except power fail/restart and system override, can be selectively

enabled, disabled, activated, deactivated, or requested under software

control. All Interrupt Control Instructions are privileged. Attempts

at execution by unprivileged programs will yield a Privilege Violation

Trap.

One RTOM is included in

all configurations. Only two of the basic integrity features and four

MPX-32 interrupts require interrupt levels on the first RTOM. These

are Power Fail/Auto Start, System Override, Console Interrupt, CALM,

Real-Time Clock, and Interval Timer. The other integrity features me

implemented using traps. Ten external interrupts are available to the

user. A maximum of two RTOMs can be used when the Scientific

Accelerator is on the system. The second RTOM provides a maximum of 14

interrupts when the Scientific Accelerator is used.

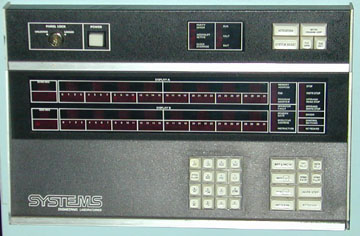

Control

Panel

The Control Panel is

included in all 32/7780 Computers. It is attached to the CPU and

provides a set of operator controls and indicators. These include the

basic functions. such as Power On/ Off, Panel Key-Lock, and the

following control operations: Run/Halt, System Reset, Attention,

Initial Program Load (IPL), and Clock Override. Function switches

provide Instruction Stop, Write, Read, Read

and Increment, Write and

Increment, Operand Read Stop, Operand Write Stop, and Keyboard

(Enable) functions.

SOFTWARE

SYSTEMS provides

four software layers.

These are:

• Operating System (MPX.32)

• Languages

• Libraries

• Tools

Each layer provides

capabilities to help reduce the cost of developing specific

application programs by helping the programmer create high quality

software that can be maintained without confusion. MPX-32, Model 1401

is a multitasking operating system that supports real-time, multibatch,

and interactive processing applications in addition to supporting the

multistream features of the 32/7780.

Languages that axe

supported under MPX-32 include FORTRAN 86+, FORTRAN 77+, Pascal,

COBOL, BASIC, and Assembly Language. Libraries are prewritten

subroutines that perform commonly used functions in the scientific,

graphic, and database applications areas, Tools help to expedite the

creation of quality software by automating key processes within the

development cycle.

CONFIGURATIONS

32/7780 NUCLEI

The 32/7780 Nuclei can

be used to configure systems to meet specific application

requirements. Each 32/7780 Nucleus includes either 1M byte or 2M bytes

of 600 nanosecond MOS Memory, a memory chassis and a logic chassis.

Cabinets, peripherals and software must be ordered separately.

The Models 2500 and

2501 are entry level systems and include a CPU and IPU. The Models

2510 and 2511 include a CPU and IPU with a pair of High-Speed

Floating-Point Units.

Maximum performance is

provided by the Models 2520-2 and 2521-2. These systems include a CPU

and IPU with a pair of High-Speed Floating-Point Units, and a pair of

Scientific Accelerators.

32/7780

PACKAGED SYSTEMS

The 32/7780 Packaged

systems are complete ready to use systems. Available with either IM

byte or 2M bytes of memory, the 32/7780 Packaged Systems include a

CPU, IPU, two High-Speed Floating-Point Units, two Scientific

Accelerators, a complement of peripherals, cabinets and the MPX-32

Operating System.

In addition, the

32/7780 Computers can be expanded and enhanced with the following

Options:

• 80-300 MB Disc

Subsystem (2535) Expands disc capacity to 300 MB per disc.

• 45-75 IPS Tape

Subsystem (2536) Replaces the standard 45 1PS Tape Drives with faster

75 IPS Tape Drives.

BENCHMARKS

A total of live

benchmarks were run on configurations based on each of the 32/7780

nuclei and the 32/7780 packaged system. (See Table 2).

The benchmarks run

were:

WHET1- General industry

wide compute bound single precision benchmark

WHET2- General industry

wide compute bound double precision benchmark

KOPBM- McDonnell

Douglas compute-bound benchmark

AEDC- Arnold Air Force

Base Engineering benchmark with balanced compute I/O

WPATT- Wright Patterson

Air Force Base benchmark with balanced compute I/O

Technology Marketing Group

Technology Marketing Group